信號(hào)發(fā)生器如何產(chǎn)生一個(gè)負(fù)脈沖?

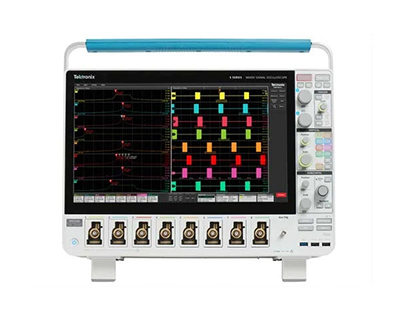

信號(hào)發(fā)生器是一種用于產(chǎn)生電子信號(hào)的設(shè)備,廣泛應(yīng)用于通信、測(cè)試和測(cè)量等多個(gè)領(lǐng)域。在現(xiàn)代電子技術(shù)中,負(fù)脈沖信號(hào)的產(chǎn)生具有重要意義,尤其是在編碼、調(diào)制和觸發(fā)電路中。本文將深入探討信號(hào)發(fā)生器是如何產(chǎn)生負(fù)脈沖信號(hào)的,以及負(fù)脈沖信號(hào)在實(shí)際應(yīng)用中的重要性。

一、信號(hào)發(fā)生器的基本原理

信號(hào)發(fā)生器的基本原理是通過控制電路的開關(guān)狀態(tài),來產(chǎn)生不同類型的信號(hào),包括正脈沖、負(fù)脈沖、正弦波、方波和三角波等。信號(hào)發(fā)生器可以通過不同的調(diào)制技術(shù)和電路配置,精確控制輸出信號(hào)的頻率、幅度和波形。

二、負(fù)脈沖的定義與特點(diǎn)

負(fù)脈沖是一種電信號(hào),其電壓值在一段時(shí)間內(nèi)低于基準(zhǔn)電壓(如0V),然后迅速恢復(fù)到基準(zhǔn)電壓。這種信號(hào)的特點(diǎn)是:

1. 極性:與正脈沖相反,負(fù)脈沖的電壓值在脈沖期間低于基準(zhǔn)值。

2. 持續(xù)時(shí)間:負(fù)脈沖的持續(xù)時(shí)間可以根據(jù)實(shí)際需求進(jìn)行調(diào)整,通常是微秒級(jí)別。

3. 幅度:負(fù)脈沖的幅度可以根據(jù)應(yīng)用需求進(jìn)行設(shè)置,有助于控制信號(hào)強(qiáng)度。

三、信號(hào)發(fā)生器產(chǎn)生負(fù)脈沖的工作原理

在信號(hào)發(fā)生器中產(chǎn)生負(fù)脈沖,一般采用以下幾種方法:

1. 反相器電路

反相器(Inverter)是一種基本的數(shù)字邏輯電路,通過將輸入信號(hào)的邏輯電平反轉(zhuǎn),可以方便地生成負(fù)脈沖。例如,輸入一個(gè)高電平(正脈沖),反相器的輸出將是低電平(負(fù)脈沖)。這種方法簡(jiǎn)單而有效,適用于低頻信號(hào)的負(fù)脈沖生成。

2. 555定時(shí)器

555定時(shí)器是一種流行的集成電路(IC),可以配置為單穩(wěn)態(tài)模式或雙穩(wěn)態(tài)模式。通過選擇適當(dāng)?shù)碾娮韬碗娙荩?55定時(shí)器可以產(chǎn)生特定持續(xù)時(shí)間的負(fù)脈沖。在單穩(wěn)態(tài)模式下,輸入觸發(fā)信號(hào)后,555定時(shí)器會(huì)輸出一個(gè)短暫的負(fù)脈沖,然后自動(dòng)返回到高電平狀態(tài)。

3. CPLD或FPGA編程

對(duì)于更復(fù)雜的應(yīng)用,可以通過可編程邏輯器件(CPLD)或現(xiàn)場(chǎng)可編程門陣列(FPGA)生成負(fù)脈沖。在這些器件中,可以使用硬件描述語言(如VHDL或Verilog)編寫代碼,設(shè)計(jì)電路邏輯,以產(chǎn)生所需的負(fù)脈沖信號(hào)。這種方法靈活性高,非常適合高頻或具有特定波形要求的應(yīng)用。

4. 數(shù)字信號(hào)控制

現(xiàn)代信號(hào)發(fā)生器通常還具備數(shù)字控制功能,可以通過軟件設(shè)置產(chǎn)生負(fù)脈沖。在用戶界面中,輸入所需的脈沖寬度、頻率和幅度后,信號(hào)發(fā)生器就能自動(dòng)生成相應(yīng)的負(fù)脈沖信號(hào)。

四、負(fù)脈沖的應(yīng)用

負(fù)脈沖信號(hào)在多個(gè)領(lǐng)域中扮演著重要角色。例如:

1. 數(shù)字通信:在數(shù)據(jù)傳輸中,負(fù)脈沖信號(hào)常用于表示邏輯0,幫助實(shí)現(xiàn)更快的信號(hào)切換。

2. 模擬電路測(cè)試:在測(cè)試放大器和其他電子組件時(shí),負(fù)脈沖可以用于檢查其響應(yīng)特性。

3. 觸發(fā)電路:負(fù)脈沖可以作為觸發(fā)信號(hào),開始其他電路的工作,如在相機(jī)閃光燈、激光發(fā)射和其他應(yīng)用中經(jīng)常使用。

信號(hào)發(fā)生器在電子設(shè)備中發(fā)揮著至關(guān)重要的作用,負(fù)脈沖信號(hào)的產(chǎn)生為各種應(yīng)用提供了便利。從簡(jiǎn)單的反相器電路到復(fù)雜的FPGA設(shè)計(jì),產(chǎn)生負(fù)脈沖的方法多種多樣。理解這些原理和技術(shù),不僅可以提高電子工程師的實(shí)際操作能力,也有助于優(yōu)化設(shè)計(jì)和測(cè)試流程。隨著科技的發(fā)展,負(fù)脈沖信號(hào)的應(yīng)用仍將不斷擴(kuò)展,為電子行業(yè)帶來更多的可能性。

關(guān)注官方微信

關(guān)注官方微信