泰克示波器在SDRAM調試中的應用

在當今嵌入式電路中,SDRAM作為高速內存使用越來越頻繁,基本上涉及到FPGA的電路都會配備幾片SDRAM存儲數據。FPGA與SDRAM之間的時序關系,是研發工程師最關心的問題,也是設計過程中面臨的最大挑戰。

SDRAM( Synchronous Dynamic Random Access Memory),同步動態隨機存儲器,同步是指Memory工作需要同步時鐘,內部的命令的發送與數據的傳輸都以它為基準:動態是指存儲陳列責要不斷的則新來保證數據不丟失:隨機是指數據不是線性依次存儲,而是自由指定地址進行數據讀寫。

一、測試背景需求

在嵌入式電路中,最常用的兩種內存是SDRAM和SRAM,其中,SRAM 讀寫方便、速度快,因為其地址線和數據線是獨立并行的,但是其內存較小,常用1Mb,而且成本較高。而SDRAM內存較大,常用64Mb、128Mb, 成本較低,但是其控制器復雜,尋址麻煩,要不斷刷新,因為其地址線和數據線是復用的。所以在嵌入式電路中SDRAM的調試更具有挑戰性,其復雜的控制器,控制信號,常常使設計者陷入麻煩之中,大大降低的開發速度,影響最終產品的上市時間。所以他們需要一種工具,也就是泰克示波器幫助他們解決問題,提高調試效率。

SDRAM調試挑戰:

1.精確的時序要求;

2. 多路信號(控制線、地址線、數據線)連調;

3.建立保持時間違規的精確定位與時間修正。

二、解決方案

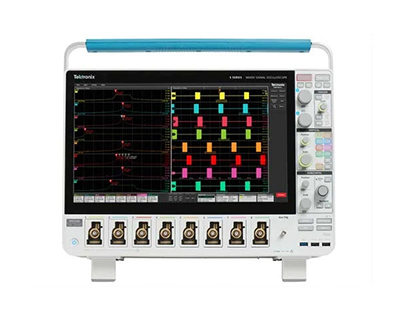

解決SDRAM的調試問題,示波器無疑是最佳選擇,但是傳統的示波器不能完全解決這類問題。泰克的MSO4000系列示波器是解決這一問題的最佳工具:

a)最多可同時測試4條模擬通道+16條數字通道;

b)模擬通道高達1GHz帶寬,5GS/s采樣率, 每通道均有10M點存儲深度;

c) 數字通道具有高達16.5GS/s的定時分辨率,精確判斷時序;

d)波形導航和搜索功能,幫助客戶快速定位關心的問題點;.

e)具有邏輯和建立保持時間違規觸發和搜索條件,給SDRAM的調試帶來極大方便。

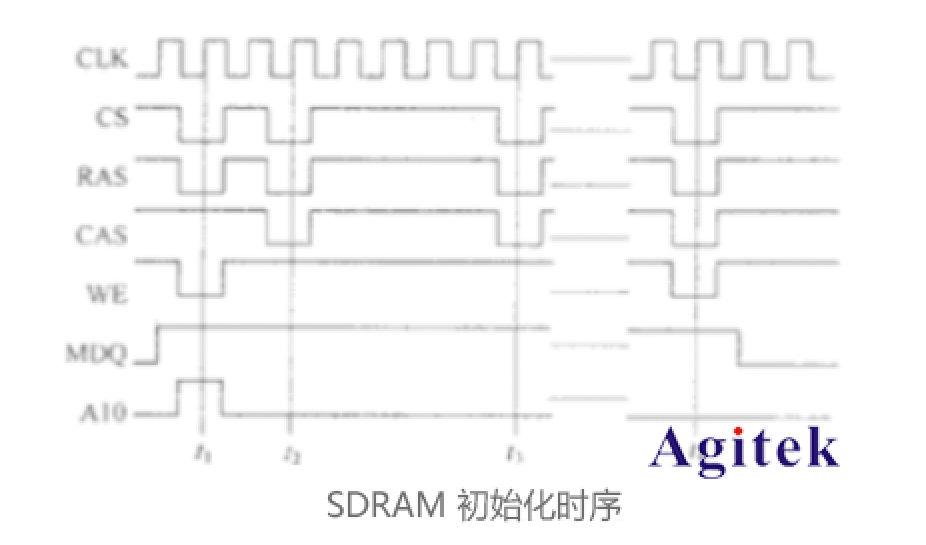

如圖所示,4個邏輯通道接SDRAM的4個控制信號,CS#片選,WE#寫使能,CSA#列選通,RAS#行選通,均為低有效。客戶關心的是,滿足: CS#=0; WE#=0; CSA#= 1; RAS#= 0時,這表示著SDRAM初始化位置,2通道的時鐘信號和4通道的數據信號的建立保持時間問題。

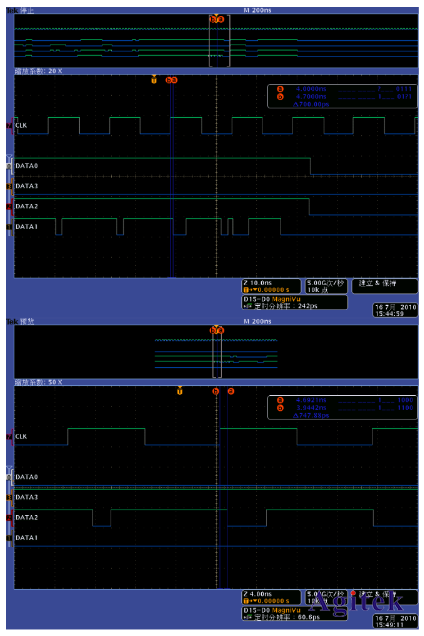

根據客戶的需求,四個邏輯信號可以按照邏輯觸發條件觸發,存儲深度可以設置成1M點或更多,觸發成功后,在存儲的信號中搜索與觸發條件- -致的情況,如圖共搜索到29個, 分別查看這29個位置,測量其建立保持時間是否滿足,如圖所示,建立時間是11.4ns, 保持時間是9ns,這個是滿足建立保持時間的,另外,客戶想知道最差的情況是出現在什么時候,也可以方便的找到。

MSO4000系列示波器可同時測試多條數據線上的的建立保持時間違規問題。如圖所示,同時測量四條數據信號的建立保持時間違規,打開MagniVu功能,高達60.6ps( 16.5GS/s)的定時分辨率,可精確地測定時鐘延與數據延的時間差。由于演示過程中的連接問題,只同時測試4條數據線,客戶的實際需求是同時測試所有數據線12bit,泰克示波器的MSO4000系列有16個邏輯通道,也可以完成這類測試。

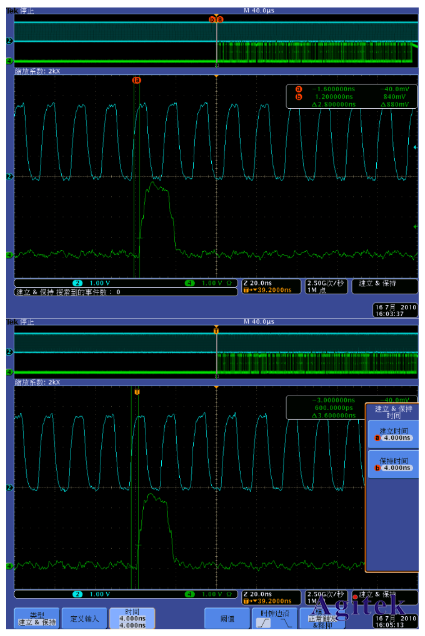

如圖所示,MSO4000系列示波器也可在模擬通道上觸發建立保持時間違規問題,可根據客戶芯片手冊的規定,設置建立時間和保持時間限值,找到信號中的問題點。但是客戶表示,最關心的還是控制信號滿足特定條件的時候,建立保持時間違規問題,對于數據線上的其他建立保持時間問題其實并不是特別重要。

以上關于泰克示波器在SDRAM調試中的應用內容由安泰測試為您分享,如果您在選型/使用過程有什么問題,歡迎登陸安泰測試。

關注官方微信

關注官方微信